“

据《韩国经济日报》报道,为了缩小与晶圆代工龙头大厂台积电在尖端制程领域的差距,三星电子已经制定了明确的制程演进计划,将于2031年正式量产1nm(SF1.0)制程。

”

据《韩国经济日报》报道,为了缩小与晶圆代工龙头大厂台积电在尖端制程领域的差距,三星电子已经制定了明确的制程演进计划,将于2031年正式量产1nm(SF1.0)制程。

报道称,三星电子晶圆代工部门预计将在2030年完成1nm半导体制程的研究与开发,然后将于2031年正式导入量产,预计量产后的1nm芯片的晶体管线宽相比三星目前最先进的2nm制程技术将缩减一半。与之对应的,三星将需要解决1nm制程所带来的物理极限挑战。为此,三星计划在缩小晶体管体积的同时,还将导入名为“叉状片”(Forks heet)技术的全新结构。

什么是Forks heet?

目前,领先的晶圆代工厂正朝着2nm(或同等)技术节点的大规模量产迈进,其中GAA纳米片晶体管技术发挥着核心作用。“环绕闸极(GAA, Gate-All-Around)” 纳米片器件架构作为FinFET技术的继任者被引入,以进一步缩小SRAM和逻辑标准单元。

而在此前的3nm制程中,三星就率先引入了GAA技术,台积电则将在2nm制程中引入。该技术主要特点是垂直堆叠两个或多个纳米片形状的导电通道,其中一个堆叠用于p,另一个堆叠用于n个器件,内嵌在逻辑标准单元内。这种配置允许设计者进一步缩小逻辑标准单元高度,即每个单元的金属线(或轨道)数量乘以金属间距。设计者还可以选择让通道更宽,以牺牲单元高度换取更大的驱动电流。除了面积缩放外,GAA纳米片晶体管相较于FinFET还有另一个优势:栅极在所有侧面包围导电通道,从而提升了通道的栅极控制,即使通道长度较短。

Forks heet技术是比利时微电子研究中心(imec)于2017年首次提出的技术架构,属于GAA技术的进阶版,其核心概念是将GAA晶体管之间的距离缩小到极限,因此在GAA当中引入绝缘的介质。

最初的Forks heet设计被称为“内壁叉状片”(Inner Wall Forksheet)——即在nMOS和pMOS晶体管之间放置绝缘介质。然而,内壁叉状片架构在量产可行性上面临多重挑战,比如:为达到90nm单元高度,介质壁厚度需控制在8-10纳米的极薄范围;介质壁在工艺早期形成,需承受后续所有前端制程的侵蚀;n/p掩模对准困难;阻碍n-p栅极连接,增加寄生电容等。

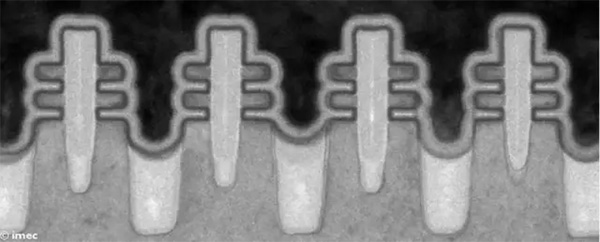

△内壁叉板器件的透射电子显微镜图像。(图片来源:imec)

针对这些制造难题,imec在2025年6月VLSI技术与电路研讨会(VLSI 2025,日本京都)上正式发布了Forksheet技术的最新进展,即“外壁叉状片”(Outer Wall Forksheet)架构,降低了工艺复杂度,带来了卓越性能,同时保持面积可扩展性。

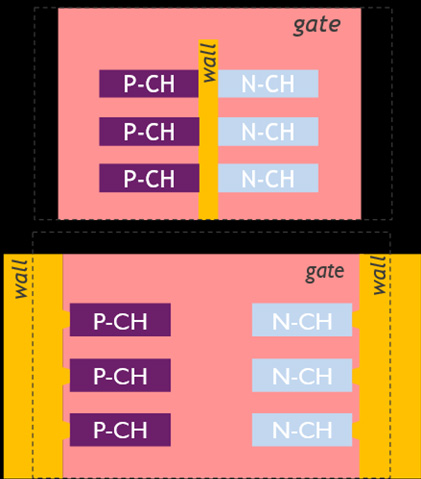

△(顶部)内壁和(下)外壁叉状片架构的示意图(来源:imec)

具体来说,“外壁叉状片”架构将绝缘壁移至标准单元边界,用于隔离同类型晶体管(p-p或n-n),而非不同类型晶体管。这使得每个绝缘壁可以与相邻的标准单元共用,绝缘壁厚度也可放宽至约15nm,不牺牲90nm的单元高度。并且绝缘壁在源/漏极形成、纳米片通道释放之后才制作,避免了早期工艺的侵蚀风险,并可采用主流的二氧化硅(SiO₂)材料。绝缘壁最终会将该堆叠分为两部分,两个极性相近的场效应晶体最终位于墙的两侧。

“外壁叉状片”架构的五个关键改进

内壁叉状片和外壁叉状片相较于GAA纳米片器件有两个共同优势:在面积扩展方面,它们都能在A10(1nm)节点实现90nm逻辑标准单元高度,优于A14(1.4nm)节点纳米片技术中的115nm单元高度;壁两侧的两个场效应晶体(内壁为n和p,外壁为n和n/或p与p)可以比基于缩尺的纳米片单元更接近,而不会导致寄生电容问题。

“外壁叉状片”相对于“内壁叉状片”有望带来五个关键方面的改进:

首先,由于绝缘壁底整合方法,绝缘壁免去了多个激进的FEOL步骤。因此,它可以由主流二氧化硅制成。在绝缘壁的最后工艺步骤中,绝缘壁体通过宽大的Si/SiGe堆叠和SiO2介质填充槽形成。

其次,由于绝缘壁被放置在单元边界,其宽度可以放宽至约15nm,从而简化工艺。

第三,一个标准单元内的n和p器件的栅极现在可以轻松连接,而无需穿越绝缘壁。

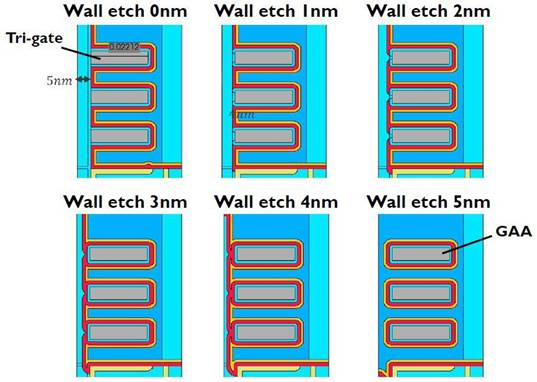

第四,“外壁叉状片”预计将优于内壁装置提供更优越的门控制,能够形成W门而非三门叉结构。更宽的绝缘壁使得在最后的RMG步骤中可以对壁面进行几纳米的蚀刻回压。这使得门极能够部分绕过通道的第四条边缘,形成一个W形门,并增强对通道的控制。通过TCAD模拟,imec研究人员发现蚀刻介质壁5nm是最优,能提升驱动电流约25%。

第五,“外壁叉状片”可以实现全通道应力——这是“内壁叉状片”架构和传统GAA纳米片难以做到的,有利于驱动电流。

根据imec的研究数据显示,相对于基于GAA纳米片技术的A14制程,基于“外壁叉状片”的A10制程基于栅间距的p-p和n-n间距缩小,SRAM单元面积减少了22%。另外,模拟数据表明,“外壁叉状片”的A10制程的全通道应力优势,使得其驱动电流相比前者提升了33%。

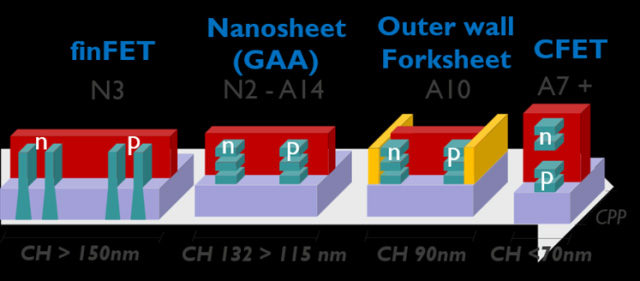

根据imec的路线图,GAA技术需要至少继续推动先进制程持续演进三代制程,之后将需要转向场效应晶体管(CFET,n型和p型晶体管垂直堆叠)技术。但由于CFET的制造复杂度极高,预计至少要到A7(7埃米)节点之后才具备量产条件。这意味着GAA纳米片时代必须至少延展到A10技术节点,该节点的单元高度预计仅为90nm。然而,在不牺牲性能的情况下压缩基于GAA纳米片的标准单元仍然具有挑战性。因此需要将Forksheet技术作为延长GAA时代的关键桥梁。这虽然不是一种颠覆性技术,是基于GAA纳米片技术的改良,但是比传统的GAA纳米片技术更大的扩展潜力。

△imec的逻辑技术路线图,展示了GAA纳米片时代从2nm到A14节点的扩展,A10节点将转向“外壁叉状片”架构,随后A7及之后的节点将会转向CFET架构。

追赶台积电的硬仗

根据TrendForce的数据,在目前的晶圆代工市场,台积电以超过70%的市场份额占据着绝对领先的地位,三星电子晶圆代工部门虽然位居全球第二,但市场份额仅7%,二者则份额上有着10倍的巨大差距。但是,三星一直并未放弃对台积电的追赶。

特别是在先进制程领域,三星一直寄希望于通过比台积电更早量产最尖端的制程工艺来争夺客户。比如,三星率先在3nm制程工艺上就引入了GAA技术架构,并于2026月30日率先宣布全球首家量产3nm芯片。但是,由于良率过低,导致三星的3nm制程在量产之后的两年多时间内一直未获得大客户的采用。

2025年年底,三星又率先量产了2nm制程。今年年初,首款基于2nm制程的Exynos 2600处理器由三星Galaxy S26系列首发搭载上市。为了满足三星自家系统LSI 事业部新款智能手机应用处理器(AP) 的生产需求,三星也正在加快全新2nm制程的研发脚步,包含预计于2026 年量产的“SF2P” 制程,以及计划于2027 年正式投入商用的“SF2P+” 制程。

更为关键的是,随着2nm制程的良率相比之前大幅提升,三星已经成功获得了特斯拉AI5/AI6芯片的订单。业内最新消息显示,三星2nm制程的最高良率已经成功突破60%,相比2025 年下半年的20% 有了显著的提升。

三星还在目前的2nm制程基础上针对大型客户的需求推出多样化的改良制程,据说为特斯拉代工的AI6芯片就将会采用定制化的“SF2T”制程。该芯片预计将从2027 年开始,于三星位于美国德州泰勒市(Taylor)的全新晶圆代工厂进行生产。

随着尖端制程良率的大幅提升,以及与大客户特斯拉的合作,市场对于三星晶圆代工部门在2026 年实现转亏为盈的目标也颇为期待。在此基础上,三星激进地提出2031年率先量产叉状片架构的1nm制程的目标,更是希望借助在尖端制程技术上的领先,实现对于台积电的强势竞争。

上一篇:【HBM之父预言:AI主导权将从GPU转向内存】

猜你喜欢