ЙиМќДЪЃКSTEP FPGA ОиеѓАДМќЧ§ЖЏ гВМўСЌНг

ЪБМфЃК2023-11-22 14:53:47 РДдДЃКЛЅСЊЭј

ЁАдкМќХЬжаАДМќЪ§СПНЯЖрЪБЃЌЮЊСЫМѕЩйI/OПкЕФеМгУЃЌЭЈГЃНЋАДМќХХСаГЩОиеѓаЮЪНЃЌЪЙгУааЯпКЭСаЯпЗжБ№СЌНгЕНАДМќПЊЙиЕФСНЖЫЃЌетбљЮвУЧОЭПЩвдЭЈЙ§4ИљааЯпКЭ4ИљСаЯпЃЈЙВ8ИіI/OПкЃЉСЌНг16ИіАДМќЃЌЖјЧвАДМќЪ§СПдНЖргХЪЦдНУїЯдЁЃ

ЁБдкМќХЬжаАДМќЪ§СПНЯЖрЪБЃЌЮЊСЫМѕЩйI/OПкЕФеМгУЃЌЭЈГЃНЋАДМќХХСаГЩОиеѓаЮЪНЃЌЪЙгУааЯпКЭСаЯпЗжБ№СЌНгЕНАДМќПЊЙиЕФСНЖЫЃЌетбљЮвУЧОЭПЩвдЭЈЙ§4ИљааЯпКЭ4ИљСаЯпЃЈЙВ8ИіI/OПкЃЉСЌНг16ИіАДМќЃЌЖјЧвАДМќЪ§СПдНЖргХЪЦдНУїЯдЁЃ

FPGAЧ§ЖЏОиеѓАДМќФЃПщЃЌЪзЯШЮвУЧРДСЫНтОиеѓАДМќЕФгВМўСЌНгЃК

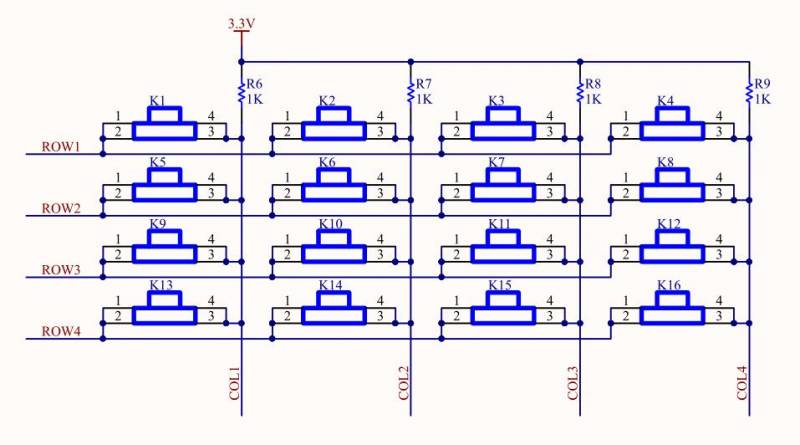

ЩЯЭМЮЊ4×4ОиеѓАДМќЕФгВМўЕчТЗЭМЃЌПЩвдПДЕН4ИљааЯпЃЈROW1ЁЂROW2ЁЂROW3ЁЂROW4ЃЉКЭ4ИљСаЯпЃЈCOL1ЁЂCOL2ЁЂCOL3ЁЂCOL4ЃЉЃЌЭЌЪБСаЯпЭЈЙ§ЩЯРЕчзшСЌНгЕНVCCЕчбЙЃЈ3.3VЃЉЃЌЖдгкОиеѓАДМќРДНВЃК

4ИљааЯпЪЧЪфШыЕФЃЌЪЧгЩFPGAПижЦРИпЛђРЕЭЃЌ

4ИљСаЯпЪ§ЪфГіЕФЃЌЪЧгЩ4ИљааЯпЕФЪфШыМААДМќЕФзДЬЌОіЖЈЃЌЪфГіИјFPGA

ЕБФГвЛЪБПЬЃЌFPGAПижЦ4ИљааЯпЗжБ№ЮЊROW1=0ЁЂROW2=1ЁЂROW3=1ЁЂROW4=1ЪБЃЌ

ЖдгкK1ЁЂK2ЁЂK3ЁЂK4АДМќЃКАДЯТЪБЖдгІ4ИљСаЯпЪфГіCOL1=0ЁЂCOL2=0ЁЂCOL3=0ЁЂCOL4=0ЃЌВЛАДЪБЖдгІ4ИљСаЯпЪфГіCOL1=1ЁЂCOL2=1ЁЂCOL3=1ЁЂCOL4=1ЃЌ

ЖдгкK5~~~K16жЎМфЕФАДМќЃКЮоТлАДЯТгыЗёЃЌЖдгІ4ИљСаЯпЪфГіCOL1=1ЁЂCOL2=1ЁЂCOL3=1ЁЂCOL4=1ЃЌ

ЭЈЙ§ЩЯУцЕФУшЪіЃКдкетвЛЪБПЬжЛгаK1ЁЂK2ЁЂK3ЁЂK4АДМќБЛАДЯТЃЌВХЛсЕМжТ4ИљСаЯпЪфГіCOL1=0ЁЂCOL2=0ЁЂCOL3=0ЁЂCOL4=0ЃЌЗёдђCOL1=1ЁЂCOL2=1ЁЂCOL3=1ЁЂCOL4=1ЃЌЗДжЎЕБFPGAМьВтЕНСаЯпЃЈCOL1ЁЂCOL2ЁЂCOL3ЁЂCOL4ЃЉжагаЕЭЕчЦНаХКХЪБЃЌЖдгІЕФK1ЁЂK2ЁЂK3ЁЂK4АДМќгІИУЪЧБЛАДЯТСЫЁЃ

АДееЩЈУшЕФЗНЪНЃЌвЛЙВЗжЮЊ4ИіЪБПЬЃЌЗжБ№ЖдгІ4ИљааЯпжаЕФвЛИљРЕЭЃЌ4ИіЪБПЬвРДЮбЛЗЃЌетбљОЭЭъГЩСЫОиеѓАДМќЕФШЋВПЩЈУшМьВтЃЌЮвУЧдкГЬађжавдет4ИіЪБПЬЖдгІзДЬЌЛњЕФ4ИізДЬЌЁЃ жСгкбЛЗЕФжмЦкЃЌИљОнЮвУЧЛљДЁНЬГЬРяПЩжЊЃЌАДМќЖЖЖЏЕФВЛЮШЖЈЪБМфдк10msвдФкЃЌЫљвдЖдЭЌвЛИіАДМќВЩбљЕФжмЦкДѓгк10msЃЌетЭЌбљШЁ20msЪБМфЁЃ20msЪБМфЖдгІ4ИізДЬЌЃЌУП5ЗжжгНјаавЛДЮзДЬЌзЊЛЛЁЃ

// -------------------------------------------------------------------- // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // -------------------------------------------------------------------- // Module: Array_KeyBoard // // Author: Step// // Description: Array_KeyBoard // // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.0 |2015/11/11 |Initial ver // -------------------------------------------------------------------- module Array_KeyBoard #( parameter NUM_FOR_200HZ = 60000 //ЖЈвхМЦЪ§ЦїcntЕФМЦЪ§ЗЖЮЇЃЌР§ЛЏЪБПЩИќИФ)( input clk_in, //ЯЕЭГЪБжг input rst_n_in, //ЯЕЭГИДЮЛЃЌЕЭгааЇ input [3:0] col, //ОиеѓАДМќСаНгПк output reg [3:0] row, //ОиеѓАДМќааНгПк output reg [15:0] key_out //ЯћЖЖКѓЕФаХКХ);/* вђЪЙгУ4x4ОиеѓАДМќЃЌЭЈЙ§ЩЈУшЗНЗЈЪЕЯжЃЌЫљвдетРяЪЙгУзДЬЌЛњЪЕЯжЃЌЙВЗжЮЊ4жжзДЬЌ дкЦфжаЕФФГвЛзДЬЌЪБМфРяЃЌЖдгІЕФ4ИіАДМќЯрЕБгкЖРСЂАДМќЃЌПЩАДЖРСЂАДМќЕФжмЦкВЩбљЗЈВЩбљ жмЦкВЩбљЪБУПИє20msВЩбљвЛДЮЃЌЖдгІетРязДЬЌЛњУПИє20msбЛЗвЛДЮЃЌУПИізДЬЌЖдгІ5msЪБМф ЖдОиеѓАДМќЪЕЯждРэВЛУїАзЕФЃЌЧыШЅСЫНтОиеѓАДМќЪЕЯждРэ */ localparam STATE0 = 2'b00; localparam STATE1 = 2'b01; localparam STATE2 = 2'b10; localparam STATE3 = 2'b11; //МЦЪ§ЦїМЦЪ§ЗжЦЕЪЕЯж5msжмЦкаХКХclk_200hz reg [15:0] cnt; reg clk_200hz; always@(posedge clk_in or negedge rst_n_in) begin if(!rst_n_in) begin //ИДЮЛЪБМЦЪ§ЦїcntЧхСуЃЌclk_200hzаХКХЦ№ЪМЕчЦНЮЊЕЭЕчЦН cnt <= 16'd0; clk_200hz <= 1'b0; end else begin if(cnt >= ((NUM_FOR_200HZ>>1) - 1)) begin //Ъ§зжТпМжагввЦ1ЮЛЯрЕБгкГ§2 cnt <= 16'd0; clk_200hz <= ~clk_200hz; //clk_200hzаХКХШЁЗД end else begin cnt <= cnt + 1'b1; clk_200hz <= clk_200hz; end end end reg [1:0] c_state; //зДЬЌЛњИљОнclk_200hzаХКХдк4ИізДЬЌМфбЛЗЃЌУПИізДЬЌЖдОиеѓАДМќЕФааНгПкЕЅаагааЇ always@(posedge clk_200hz or negedge rst_n_in) begin if(!rst_n_in) begin c_state <= STATE0; row <= 4'b1110; end else begin case(c_state) STATE0: begin c_state <= STATE1; row <= 4'b1101; end //зДЬЌc_stateЬјзЊМАЖдгІзДЬЌЯТОиеѓАДМќЕФrowЪфГі STATE1: begin c_state <= STATE2; row <= 4'b1011; end STATE2: begin c_state <= STATE3; row <= 4'b0111; end STATE3: begin c_state <= STATE0; row <= 4'b1110; end default:begin c_state <= STATE0; row <= 4'b1110; end endcase end end //вђЮЊУПИізДЬЌжаЕЅаагааЇЃЌЭЈЙ§ЖдСаНгПкЕФЕчЦНзДЬЌВЩбљЕУЕНЖдгІ4ИіАДМќЕФзДЬЌЃЌвРДЮбЛЗ always@(negedge clk_200hz or negedge rst_n_in) begin if(!rst_n_in) begin key_out <= 16'hffff; end else begin case(c_state) STATE0:key_out[3:0] <= col; //ВЩМЏЕБЧАзДЬЌЕФСаЪ§ОнИГжЕИјЖдгІЕФМФДцЦїЮЛ STATE1:key_out[7:4] <= col; STATE2:key_out[11:8] <= col; STATE3:key_out[15:12] <= col; default:key_out <= 16'hffff; endcase end end endmodule

БОНкжївЊЮЊДѓМвНВНтСЫОиеѓАДМќЕФЙЄзїдРэМАШэМўЩшМЦЃЌашвЊДѓМвеЦЮеЕФЭЌЪБздМКДДНЈЙЄГЬЃЌЭЈЙ§ећИіЩшМЦСїГЬЃЌЩњГЩFPGAХфжУЮФМўМгдиВтЪдЁЃ

ЗжЯэЕНЃК

ВТФуЯВЛЖ